# Low phase noise and low jitter 0.1-10GHz VCO

David Ruffieux, senior expert & head of system-on-chip research

Swiss Center for Electronics and Microtechnology, CSEM

david.ruffieux@csem.ch

Lausanne, 28.06.2018

#### **Outline**

- Introduction & Motivations

- Q-factor definition and calculation

- Review of classical VCO topologies

- Discussion on phase noise and LC tank design

- Choice of L and C<sub>V</sub> to optimize phase noise power performances

- Presentation of low voltage VCO structure suitable for high swings

- 2.4GHz 65nm CMOS BLE VCO measurement results

- Alternative synthesizer architecture based on FBAR

- Performance comparison with LC/XO PLL

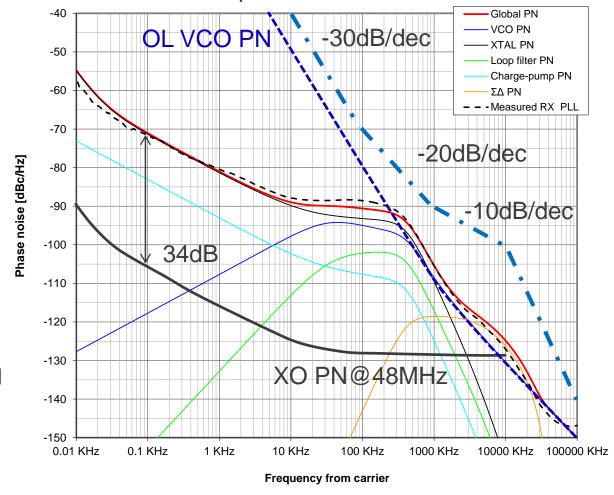

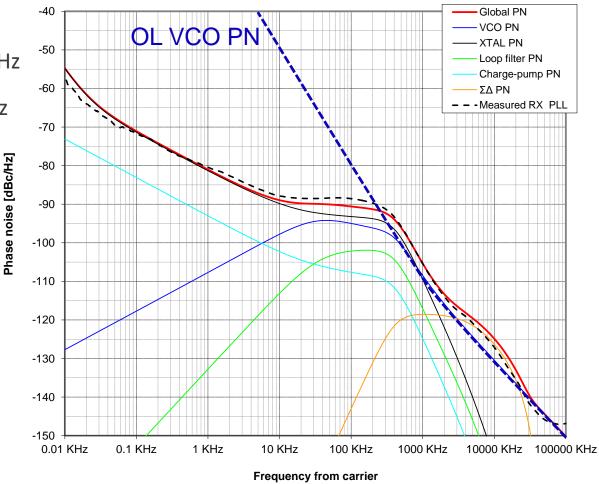

## PLL performance is limited by XTAL and VCO phase noise

#### Close-in noise limited by:

- XO phase noise

- Increased by 20 log(N)

#### Far-from-carrier noise by:

VCO phase noise

#### **PLL Loop BW**

Chosen when those noise sources are equal

#### 2.4GHz PLL phase noise with 48MHz XO

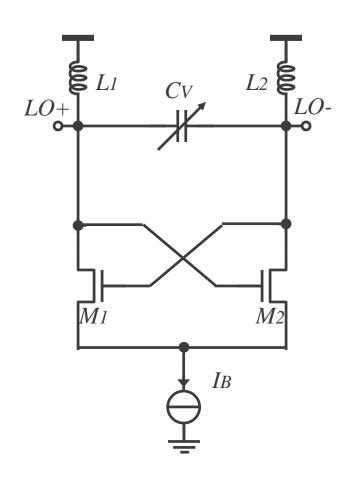

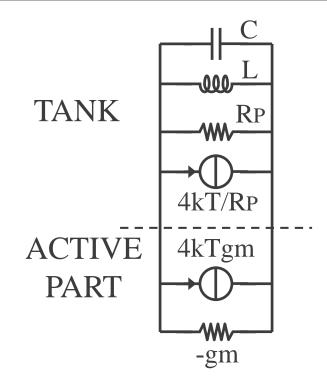

# **Simple VCO structure**

- Cross-coupled pair provides negative conductance

- $-g_m/2$  with  $g_m = I_B/(2 \cdot n \cdot U_T)$  in sub-T

- Should balance tank loss  $(g_p=1/R_p)$

- Calc R<sub>p</sub> with series/parallel transformation

- Large swing feasible (~2·V<sub>CC</sub>)

- Barkhausen criterion

$$\omega_o = \sqrt{\frac{1}{L \cdot C}}$$

$g_m \cdot R_P = -1$

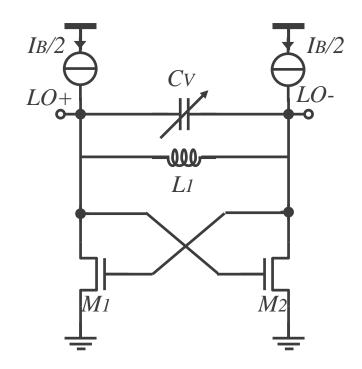

## **Another simple VCO structure**

- Current can be fed on both drains if only a 2 terminals single coil is available

- Drain junction cap loading tank

- Limited swing (V<sub>CC</sub>-V<sub>DSAT</sub>)/2

- Feed inductor midpoint instead

- Same V<sub>OSC</sub>(I<sub>B</sub>) as calculated for XO

- Large swing feasible

- What happens if constant V<sub>CC</sub> bias?

- Current keeps increasing until M<sub>1,2</sub>

leave saturation

- Strong non-linearity reduces gain

- Leads to increased phase noise

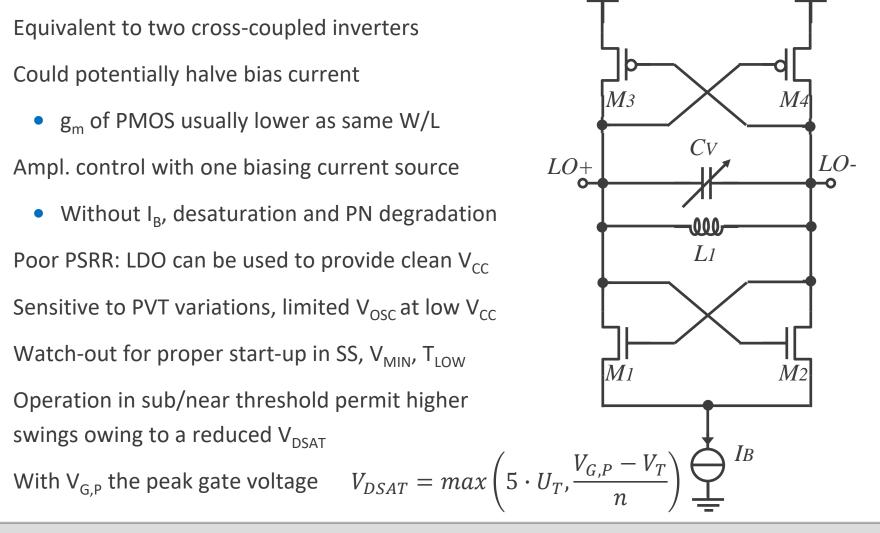

# **Complementary VCO structure (most popular)**

- Equivalent to two cross-coupled inverters

- Could potentially halve bias current

- g<sub>m</sub> of PMOS usually lower as same W/L

- Ampl. control with one biasing current source

- Without I<sub>R</sub>, desaturation and PN degradation

- Poor PSRR: LDO can be used to provide clean  $V_{CC}$

- Sensitive to PVT variations, limited  $V_{OSC}$  at low  $V_{CC}$

- Watch-out for proper start-up in SS, V<sub>MIN</sub>, T<sub>LOW</sub>

- Operation in sub/near threshold permit higher swings owing to a reduced V<sub>DSAT</sub>

# How to optimize the phase noise power product of a VCO

Noise

$$\phi_{n} = \frac{(1+\gamma) \cdot kT}{Q} \cdot \sqrt{\frac{L}{C}} \cdot \left(\frac{\omega_{o}}{\Delta \omega}\right)^{2} \cdot \frac{1}{V_{OSC}^{2}}$$

Power

$$I_{OSC} \cdot V_{DD} \rightarrow \frac{V_{OSC} \cdot V_{DD}}{\sqrt{\frac{L}{C}} \cdot Q} \Big|_{V_{OSC} >> 0}$$

Noise x Power

$$\phi_n \cdot P_{OSC} \propto \frac{\left(1+\gamma\right)}{Q^2} \cdot \frac{V_{DD}}{V_{OSC}}$$

#### To get lower PN

- 1. Max Q

- 2. Max V<sub>OSC</sub>

- 3. Min  $\gamma$

- 4. Increase C

$$\omega_o = \sqrt{\frac{1}{L \cdot C}}$$

$$g_m \cdot R_P = -1$$

# How to design the VCO tank? (obviously an iterative process!)

Selection of coil type

External coil

Q up to 100, up to 2-3GHz, reproducibility of PCB

Bondwire Very good Q but reproducibility issues (L=1nH/mm)

PCB trace, microstrip line

Suitable for SHF, IO modelling + ESD issues

Integrated Attractive above 1GHz, Q~10-20@ 2.4GHz

Determine the fixed VCO load (C<sub>F</sub>) mixers & PA, buffers, PLL dividers, VCO, routing

Varactor C<sub>V</sub> need to cover desired BW & all manufacturing tolerances

• Using

$$k = \frac{C_F + C_{V,MAX}}{C_F + C_{V,MIN}}$$

and  $k' = \frac{C_{V,MAX}}{C_{V,MIN}}$

$$\frac{\Delta f}{f} = \frac{1}{2} \cdot \left(\frac{\Delta C}{C} + \frac{\Delta L}{L} + BW\right)$$

The tuning range and the min varactor size can be expressed as

$$TR = \pm \frac{f_{MAX} - f_{MIN}}{f_{MAX} + f_{MIN}} = \pm \frac{\sqrt{k} - 1}{\sqrt{k} + 1}$$

$C_{V,MIN} = \left(\frac{k - 1}{k' - k}\right) \cdot C_F$

• The max possible inductor value can be determined, phase noise perfs estimated

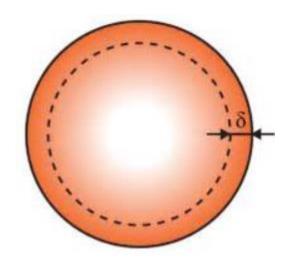

# Coil Q-factor limitation due to skin depth effect

Skin depth simplified calculation

$$\delta = \sqrt{rac{2

ho}{(2\pi f)(\mu_0\mu_r)}}pprox 503\,\sqrt{rac{

ho}{\mu_r f}}$$

- For copper,  $\mu_r = 1$ ,  $\rho = 1.68E-8 \Omega \cdot m$

- $\delta = 1.33 \, \mu m @ 2.4 \, GHz$

- $\delta = 0.27 \, \mu m @ 60 \, GHz$

- It can't be neglected

- Use EM solver to study impact more carefully (e.g. Momentum)

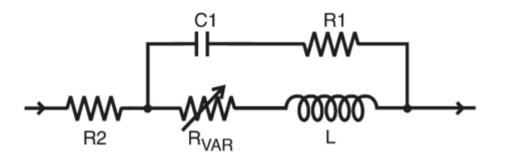

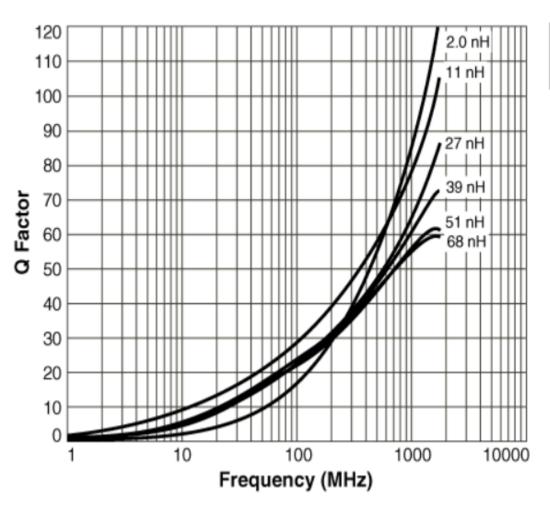

# **Equivalent model for discrete coils**

- R<sub>2</sub> is DC resistance

- R<sub>VAR</sub> accounts for skin effect

$$R_{VAR} = \mathbf{k} \cdot \sqrt{f}$$

k in  $[\Omega \cdot \mathbf{s}^{0.5}]$

- C<sub>1</sub> defines Self Resonance Frequency

- R<sub>1</sub> & R<sub>VAR</sub> define Q @ SRF

Upper

| Part number | <b>R1</b><br>(Ω) | <b>R2</b> (Ω) | C(pF) | L(nH) | k        | limit<br>(MHz) |

|-------------|------------------|---------------|-------|-------|----------|----------------|

| 0402HP-1N0  | 6                | 0.038         | 0.030 | 1.00  | 2.70E-06 | 20000          |

| 0402HP-2N0  | 5                | 0.038         | 0.050 | 2.00  | 5.22E-06 | 20000          |

| 0402HP-2N2  | 4                | 0.038         | 0.040 | 2.20  | 5.70E-06 | 20000          |

| 0402HP-2N4  | 13               | 0.042         | 0.044 | 2.40  | 6.20E-06 | 20000          |

| 0402HP-2N7  | 11               | 0.056         | 0.044 | 2.70  | 6.46E-06 | 20000          |

| 0402HP-3N3  | 15               | 0.045         | 0.032 | 3.30  | 7.80E-06 | 20000          |

| 0402HP-3N6  | 10               | 0.045         | 0.022 | 3.60  | 8.10E-06 | 20000          |

| 0402HP-3N9  | 12               | 0.045         | 0.042 | 3.90  | 9.70E-06 | 14000          |

| 0402HP-4N3  | 10               | 0.040         | 0.048 | 4.30  | 1.12E-05 | 12000          |

| 0402HP-4N7  | 13               | 0.060         | 0.052 | 4.70  | 1.29E-05 | 12000          |

# **Typical discrete 402 coil Q-factor and Self Resonance Frequency**

| Inductance <sup>2</sup> (nH) | Percent<br>tol <sup>3</sup> | 900 MHz |                    | 1.7 GHz |                    | SRF typ |

|------------------------------|-----------------------------|---------|--------------------|---------|--------------------|---------|

|                              |                             | L typ   | Q typ <sup>4</sup> | L typ   | Q typ <sup>4</sup> | (GHz)   |

| 1.0                          | 5                           | 0.97    | 46                 | 0.99    | 72                 | 16.0    |

| 2.0                          | 5                           | 1.96    | 58                 | 1.98    | 85                 | 15.2    |

| 2.2                          | 5                           | 2.17    | 60                 | 2.17    | 86                 | 15.1    |

| 2.4                          | <b>5</b> ,3, <b>2</b>       | 2.37    | 60                 | 2.38    | 83                 | 14.0    |

| 2.7                          | <b>5</b> ,3, <b>2</b>       | 2.66    | 62                 | 2.68    | 85                 | 13.0    |

| 3.3                          | <b>5</b> ,3, <b>2</b>       | 3.26    | 66                 | 3.28    | 95                 | 12.8    |

| 3.6                          | <b>5</b> ,3, <b>2</b>       | 3.56    | 65                 | 3.58    | 94                 | 11.7    |

| 3.9                          | <b>5</b> ,3, <b>2</b>       | 3.87    | 64                 | 3.91    | 98                 | 9.50    |

| 4.3                          | <b>5</b> ,3, <b>2</b>       | 4.26    | 63                 | 4.33    | 90                 | 7.15    |

| 4.7                          | <b>5</b> ,3, <b>2</b>       | 4.67    | 58                 | 4.74    | 83                 | 6.85    |

| 5.1                          | <b>5</b> ,3, <b>2</b>       | 5.07    | 54                 | 5.16    | 76                 | 6.80    |

|                              |                             |         |                    |         |                    |         |

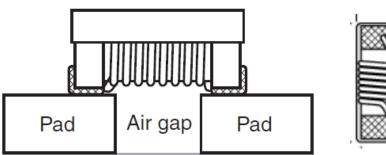

#### **Integrated coils**

- Use Al RDL (aluminum redistribution layer) + ultra-thick metal process option

- Use RF-PDK coil generator to get expected peformances

- Usually limited to single layer coil

- Designing your own coil is feasible but requires expertise and is time-consuming

- Use EM-solver such as e.g. Momentum

- Difficult to guarantee error free design (LVS is tricky)

- Multi-layer coils and transformers can be engineered

- Typical performance of a compact integrated coil at 2.4GHz

- L=7.9nH, R=8 $\Omega$ , Q=13, SRF=7.5GHz, C<sub>SRF</sub>=65fF, C<sub>TOT</sub>=637fF

- A wider area could lead to better performances

#### Varactor design

- There are different types of analog varactors

- Junction diodes, Inversion & accumulation MOS capacitance

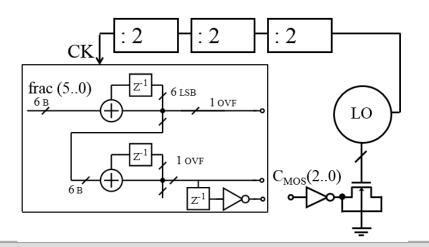

- Digitally-controlled varactors can be made with

- MOM cap and switches

- Inversion capacitance

- Combined analog and digitally controlled varactor for fine and coarse tuning

- DCO using  $2^{nd}$  order  $\Delta\Sigma$  modulator on 3-unit caps for fine frequency interpolation

- Varactor tuning ratio and Q-factor is a compromise

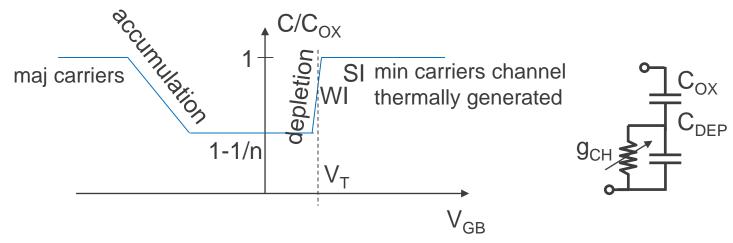

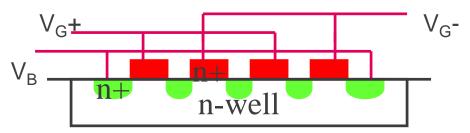

# **Analog varactor using MOS capacitor (I)**

NMOS C(V) curve (neglecting overlap capacitance)

- Inversion or depletion capacitance has very abrupt C(V) change leading to high gain

- Place substrate tap regularly to provide maj carriers as well to prevent Q degradation

- Q scales as 1/L<sup>2</sup>, watch out for R<sub>G</sub> (W)

- Overlap capacitance limit CM/Cm

- Alternate + & fingers (virtual gnd)

- No contact required in active zone

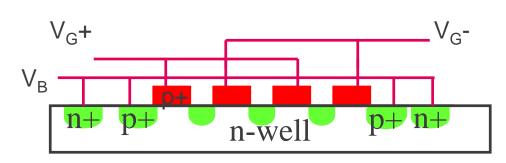

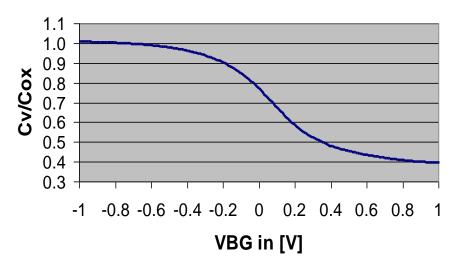

# **Analog varactor using MOS capacitor (II)**

- Accumulation varactor has lower and more linear dC/dV curve than inversion

- dC/dV curve is max near 0V bias provided G and S/D doping is reverted

$Cv_{M} / Cv_{m} = 2.6$  (I= 0.46  $\mu$ m in 0.18  $\mu$ m CMOS)

- Equivalent to NMOS in NW or PMOS in PW using triple well

- Inverse doping shifts curve by V<sub>BG</sub>

- Q scales as 1/L<sup>2</sup>, watch out for R<sub>G</sub> (W)

- Overlap capacitance limit CM/Cm

- Alternate + & fingers (virtual gnd)

- No contact required in active zone

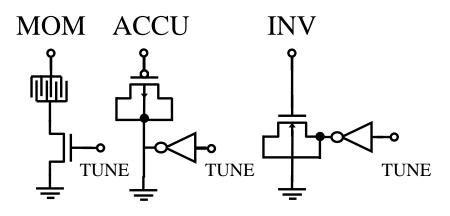

#### **Digitally controlled varactor**

- Finger type fringe MOM capacitor with MOS switch (no V<sub>CC</sub>, V<sub>CM</sub> dependency on C)

- Size switch properly to get desired Q (1/Ron=β·(V<sub>CC</sub>-V<sub>T</sub>))

- Parasitic cap (MOS + fringe cap) determines on/off ratio

- Accumulation (switch shorted SDB terminals) or inversion (switch SD) MOSCAP

- Beware of the common mode potential to operate in low gain zone

- Frequency interpolation can be obtained with  $\Delta\Sigma$  modulator for fine tuning

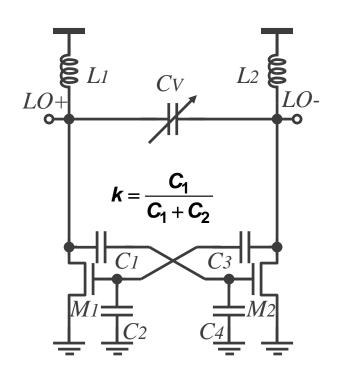

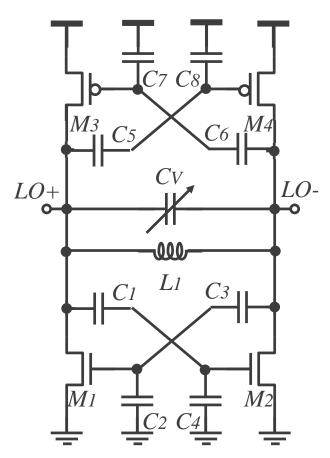

# How to get large swings: VCO core structure using cap attenuation

Use capacitive attenuation, k, to

- Linearize MOS and control its biasing

- Negative gm, V<sub>OSC</sub> are scaled by 1/k

- Permit WI operation

- Decouple drain and gate voltages at DC

- High V<sub>OSC</sub> / V<sub>CC</sub> ratio

- $V_{OSC,MAX} = V_{CC} V_{DSAT}$

- No PVT influence on V<sub>OSC</sub>

- Suitable for very low V<sub>CC</sub> operation

- 0.5V VCO with 0.7V diff 0-to-peak feasible

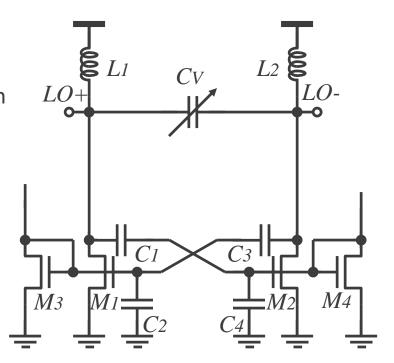

## Biasing of the VCO core structure using cap attenuation (I)

- Gate biasing with diode-connected MOS

- I<sub>VCO</sub> set by mirror ratio (use a fraction for M<sub>3,4</sub>)

- g<sub>m</sub> loss scaled by square of attenuation factor

- Resistors can be used to make diode connection

- Cap at the drain nodes is at CM voltage

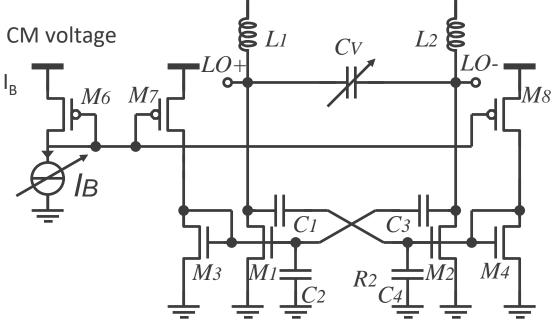

# Biasing of the VCO core structure using cap attenuation (II)

- Gate biasing with diode-connected MOS

- I<sub>VCO</sub> set by mirror ratio (use a fraction for M<sub>3,4</sub>)

- g<sub>m</sub> loss scaled by square of attenuation factor

- Resistors can be used to make diode connection

- Cap at the drain nodes is at CM voltage

- Add M<sub>6,7,8</sub> mirrors to control via I<sub>B</sub>

- Similar I(V<sub>OSC</sub>) behaviour as that derived for XO

$$I_{D_{1\omega}}(A) \frac{I_{\mathcal{B}0}\left(\frac{A}{n \cdot U_T}\right)}{2 \cdot I_{\mathcal{B}1}\left(\frac{A}{n \cdot U_T}\right)} = \overline{I_D}(A)$$

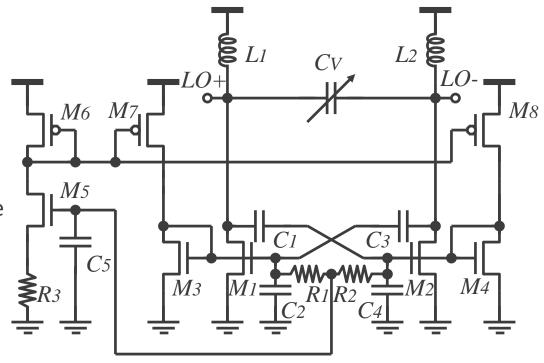

# **Complete VCO structure including AGC loop**

#### Amplitude regulation formed by

- R1,R2,C5 (BW)

- M5,R3 (PTAT I<sub>REF</sub>)

#### **Benefits**

- constant amplitude

- insensitive to dQ, dC

- Suppression of amplitude noise

- Min AM to PM conversion

- 1/f noise of M<sub>1,2</sub>

- Min power consumption

- Great design freedom

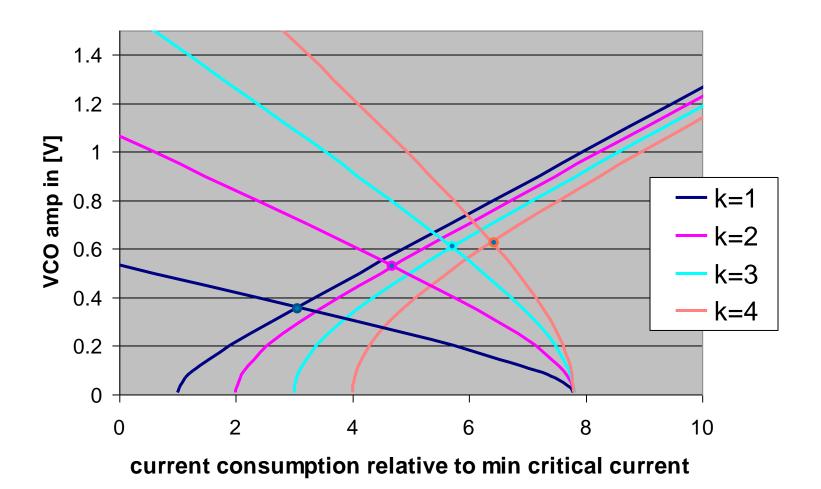

# V<sub>OSC</sub> vs I for VCO & REG and different k values

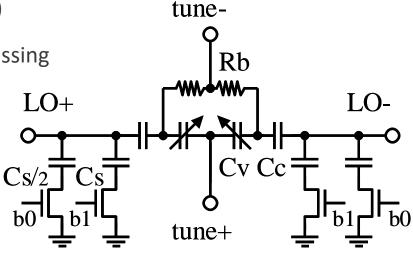

#### **Details of the varactors implementation**

- AC-coupled accumulation varactors can be used (dC/dV max near 0V!)

- Yields differential tuning (good at low V<sub>CC</sub>)

- Much better PSRR

- Size properly the resistors (Q-degradation)

- Study common-mode behaviour to add missing elements & watch-out for added pole!

- Coarse tuning obtained with SC-C<sub>MOM</sub>

- Ensure sufficient overlap with C<sub>V,ANA</sub>

- Obviously more than 2 bits feasible

# **Complementary AC-coupled VCO topology**

- Relaxed phase noise or V<sub>OSC</sub> requirements ?

- Complementary structure may halve P<sub>DISS</sub>

- $V_{OSC}$  up to  $(V_{CC} V_{DSAT})/2$

- Implement biasing, AGC and CM ctrl loops

- Truly low voltage structure

- V<sub>CC</sub> = 1V over PVT in production

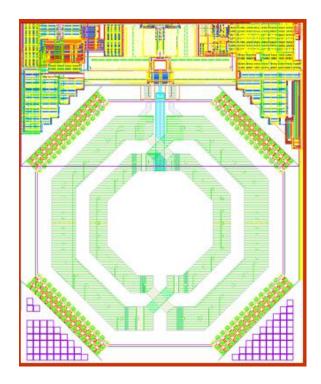

## Layout view and things to care about (65nm CMOS)

- Calculate loaded-Q and equivalent series resistor

- Size routing lines adequately (R vs C trade-off)

- Perform layout extract (RC)

- Investigate where the energy flows

- Make good virtual ground

- Optimize Q of each branch

- Evaluate biasing resistors cut-off

- DC noise up-converted but R<sub>RF</sub> << R<sub>DC</sub>!

- Connect both gate ends of MOS

- Calculate R<sub>GATE</sub> to find max W<sub>G</sub>

- Watch-out for vias, evaluate their resistance

VCO is ~50% of PLL area ~0.2x0.3mm<sup>2</sup>

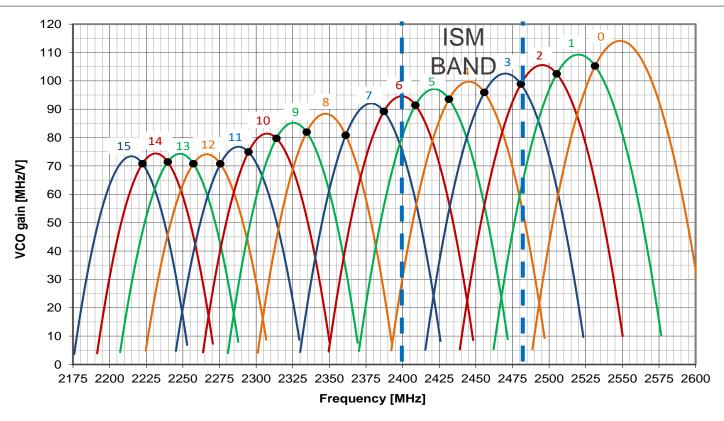

## Measurements of the VCO gain across its sub-bands

- Wide frequency range with 16 sub-bands (±9%)

- Very good overlap

- Almost constant KVCO over 2.4-2.48GHz

# 2.4GHz PLL phase noise with 48MHz XO and consumption

#### **VCO** noise

- 1/f noise corner as high as 1MHz

- PN of -110dBc/Hz @  $\Delta f = 1MHz$

#### **Current consumption**

- VCO 850μA

- XO wi buffer 100 μA

- Total PLL 1.5mA

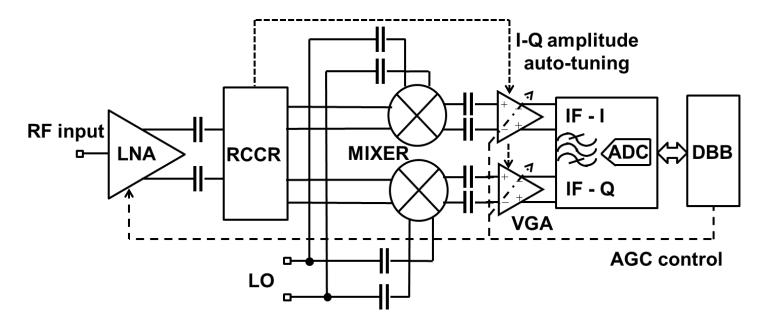

# **Quadrature generation**

2 cross-coupled VCOs

Doubles the power & area, L matching

LO @ carrier frequency & phase shifter • Power dissipation, Q degradation + limiter (RC-CR)

• LO @  $2 \cdot f_C \& \div 2$  in quadrature

Avoids LO pulling, usually better Q, higher power since load is not absorbed by tank

Phase shifter in RX path

Linearity, noise figure, LO pulling

#### **Avoiding quadrature generation**

- Since quadrature is not required in TX, use RC-CR phase shifter in signal path

- High LNA gain to mitigate 3dB RC-CR loss and NF of passive mixers

- Compromise on linearity

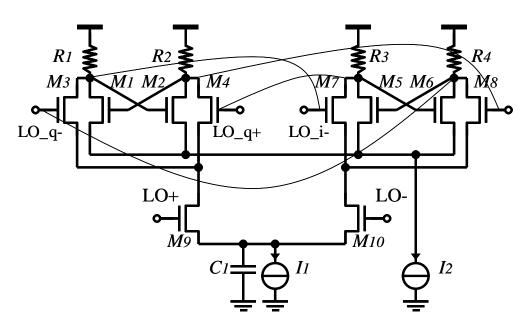

## Quadrature LO generation with source coupled logic divider

# Small signal Kirchhoff equations

$$\begin{bmatrix}

1/R_{1,2} - gm_{1,2} + s \cdot Cp_{1,2} \\

- gm_{3,4}

\end{bmatrix}$$

$$\begin{bmatrix} 1/R_{1,2} - gm_{1,2} + s \cdot Cp_{1,2} & gm_{7,8} \\ -gm_{3,4} & 1/R_{3,4} - gm_{5,6} + s \cdot Cp_{3,4} \end{bmatrix} \cdot \begin{bmatrix} V_{1,2} \\ V_{3,4} \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \end{bmatrix}$$

#### Barkhausen criterion

$$(1/R_{1,2} - gm_{1,2}) \cdot (1/R_{3,4} - gm_{5,6}) = 0$$

$$s^2 \cdot Cp_{1,2} \cdot Cp_{3,4} - (j)^2 \cdot gm_{3,4} \cdot gm_{7,8} = 0$$

# Large signal equations

$$\hat{V} = 2 \cdot \frac{I_{M1}}{gm_{1,crit}} = 2 \cdot R \cdot I_{M1}$$

$$\omega_{o} = \frac{gm_{3}}{C} \cdot \frac{I_{M1,crit}}{I_{M1}} \rightarrow \frac{2 \cdot I_{M3}}{C \cdot \hat{V}}$$

if  $\omega$ o close to  $\omega_{LO}/2$ , injection locking